# WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEH000802ALPP5N00000

# **OLED Specification**

| Conte | ents www.winstar.com.tw                                  |

|-------|----------------------------------------------------------|

| 5     | Module Classification Information                        |

| 6     | General Specification                                    |

| 6     | Absolute Maximum Ratings                                 |

| 7     | Electrical Characteristics                               |

| WIN   | WINSTAR Display<br>華凌光電股份有限公司<br>ISTAR                   |

| 7     | Optical Characteristics                                  |

| 8     | Interface Pin Function                                   |

| 9     | Counter Drawing & Block Diagram                          |

| 11    | Function Description                                     |

| 24    | Character Generator ROM Pattern                          |

| 28    | Instruction Table                                        |

| 29    | Timing Characteristics                                   |

| 32    | Initializing of LCM                                      |

| 51    | OLED Life Time                                           |

| Tech  | nology - Innovation - Value<br>Eco Friendly - Revolution |

| 52    | Reliability                                              |

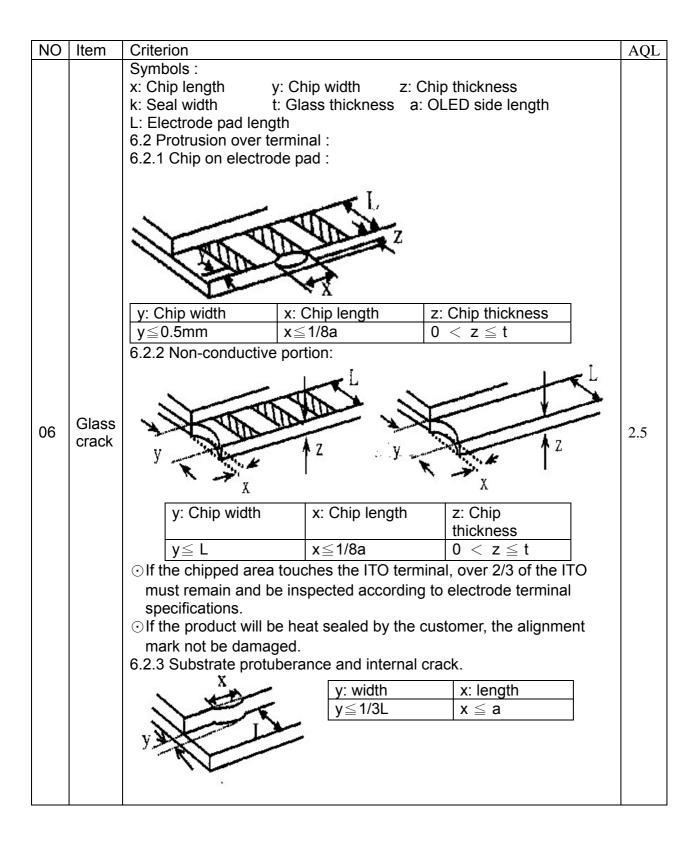

| 54    | Inspection specification                                 |

| 60    | Precautions in use of OLED Modules                       |

# **SPECIFICATION** Version: A

| CU | CT |   | N/I | D |   |  |

|----|----|---|-----|---|---|--|

| CU |    | U | IVI |   | • |  |

MODULE NO.: WEH000802ALPP5N00000

| APPROVED BY:            |  |

|-------------------------|--|

| (FOR CUSTOMER USE ONLY) |  |

| SALES BY    | APPROVED BY | CHECKED BY | PREPARED BY |

|-------------|-------------|------------|-------------|

|             |             |            |             |

|             |             |            |             |

|             |             |            |             |

| SSUED DATE: |             |            |             |

# MODLE NO:

| REC     | ORDS OF REV              | DOC. FIRST ISSUE       |                               |

|---------|--------------------------|------------------------|-------------------------------|

| VERSION | DATE                     | REVISED<br>PAGE<br>NO. | SUMMARY                       |

| 0<br>A  | 2010/11/18<br>2010.12.20 | 10                     | First issue<br>68 series only |

|         |                          |                        |                               |

|         |                          |                        |                               |

# 1. Module Classification Information

#

| 1  | Brand: WINS       | Brand: WINSTAR DISPLAY CORPORATION           |                        |  |  |  |  |

|----|-------------------|----------------------------------------------|------------------------|--|--|--|--|

| 2  | E: OLED           | E: OLED                                      |                        |  |  |  |  |

| 3  | Display Type      | : H→Character Type, G→Graph                  | іс Туре                |  |  |  |  |

| 4  | Number of do      | ts: 8 characters, 2Lines.                    |                        |  |  |  |  |

| 5  | Serials code      |                                              |                        |  |  |  |  |

|    |                   | A : Amber B : Blue                           | R : RED C : Full color |  |  |  |  |

| 6  | 6 Emitting Color  | G : Green                                    | W : White              |  |  |  |  |

|    |                   | Y: Yellow Green                              | L: Yellow              |  |  |  |  |

| 7  | Polarizer         | P: With Polarizer; N: Without Polarizer      |                        |  |  |  |  |

| 8  | Display<br>Mode   | P : Passive Matrix ; A: Active Matrix        |                        |  |  |  |  |

| 9  | Driver<br>Voltage | 3: 3.0 V; 5: 5.0V                            |                        |  |  |  |  |

| 10 | Touch Panel       | N : Without touch panel; T: With touch panel |                        |  |  |  |  |

| 11 | Serial No.        | 00000: Sales code                            |                        |  |  |  |  |

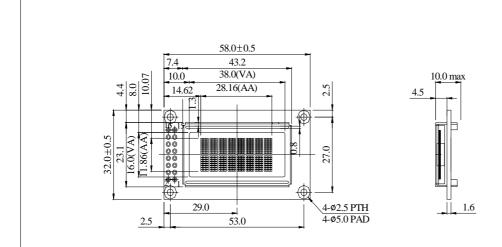

# 2. General Specification

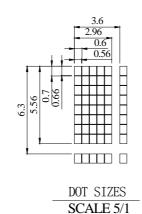

| Item                 | Dimension               | Unit |

|----------------------|-------------------------|------|

| Number of Characters | 8 characters x 2 Lines  | _    |

| Module dimension     | 58.0 x 32.0 x 10.0(MAX) | mm   |

| View area            | 38.0 x 16.0             | mm   |

| Active area          | 28.16 x 11.86           | mm   |

| Dot size             | 0.56 x 0.66             | mm   |

| Dot pitch            | 0.60x 0.70 mm           |      |

| Character size       | 2.96 x 5.56             | mm   |

| Character pitch      | 3.6 x 6.3               | mm   |

| LCD type             | OLED , Yellow           | 1    |

| Duty                 | 1/16                    |      |

# 3. Absolute Maximum Ratings

| Item                     | Symbol              | Min  | Max | Unit                   | Notes |

|--------------------------|---------------------|------|-----|------------------------|-------|

| Operating Temperature    | T <sub>OP</sub>     | -40  | +80 | $^{\circ}$ C           |       |

| Storage Temperature      | T <sub>ST</sub>     | -40  | +80 | $^{\circ}\!\mathbb{C}$ |       |

| Input Voltage            | Vı                  | -0.3 | VDD | V                      |       |

| Supply Voltage For Logic | VDD-V <sub>SS</sub> | -0.3 | 5.3 | V                      |       |

# 4. Electrical Characteristicsical

| Item                     | Symbol  | Condition    | Min     | Тур  | Max     | Unit |

|--------------------------|---------|--------------|---------|------|---------|------|

| Supply Voltage For Logic | VDD-VSS | _            | 3.0     | 5.0  | 5.3     | V    |

| Input High Volt.         | VIH     | _            | 0.9 VDD | _    | VDD     | V    |

| Input Low Volt.          | VIL     | _            | GND     | _    | 0.1VDD  | V    |

| Output High Volt.        | VOH     | IOH=-0.5mA   | 0.8 VDD | _    | VDD     | V    |

| Output Low Volt.         | VOL     | IOL=0.5mA    | GND     | _    | 0.2 VDD | V    |

| Supply Current           | IDD     | VDD=5V       | _       | 16   | _       | mA   |

| CIEx(Yellow)             |         | x,y(CIE1931) | 0.44    | 0.48 | 0.52    |      |

| CIEy(Yellow)             |         | x,y(CIE1931) | 0.46    | 0.50 | 0.54    |      |

# **5. Optical Characteristics**

| Item                                                     | Symbol | Condition      | Min    | Тур | Max | Unit |

|----------------------------------------------------------|--------|----------------|--------|-----|-----|------|

|                                                          | (V)θ   |                | 160    |     |     | deg  |

| View Angle                                               | (Η)φ   |                | 160    |     |     | deg  |

| Contrast Ratio                                           | CR     | Dark           | 2000:1 |     | _   | _    |

| Response Time                                            | T rise | _              |        | 10  |     | μs   |

|                                                          | T fall | _              |        | 10  |     | μs   |

| Supply Voltage For Logic 5V 50% CheckBoard Brightness    |        | With polarizer |        | 125 |     | nits |

| Supply Voltage For Logic 3V<br>50% CheckBoard Brightness |        | With polarizer |        | 175 |     | nits |

# 6. Interface Pin Function

| Pin No. | Symbol | Level | Description                              |

|---------|--------|-------|------------------------------------------|

| 1       | VSS    | 0V    | Ground                                   |

| 2       | VDD    | 5.0V  | Supply Voltage for logic                 |

| 3       | NC     | _     |                                          |

| 4       | RS     | H/L   | H: DATA, L: Instruction code             |

| 5       | R/W    | H/L   | H: Read(MPU→Module) L: Write(MPU→Module) |

| 6       | E      | H,H→L | Chip enable signal                       |

| 7       | DB0    | H/L   | Data bit 0                               |

| 8       | DB1    | H/L   | Data bit 1                               |

| 9       | DB2    | H/L   | Data bit 2                               |

| 10      | DB3    | H/L   | Data bit 3                               |

| 11      | DB4    | H/L   | Data bit 4                               |

| 12      | DB5    | H/L   | Data bit 5                               |

| 13      | DB6    | H/L   | Data bit 6                               |

| 14      | DB7    | H/L   | Data bit 7                               |

| 15      | NC     | _     |                                          |

| 16      | NC     | _     |                                          |

# **%Brightness Control**

| Brightness(nits) | Power consumption(measured with random texts) |

|------------------|-----------------------------------------------|

| 125(typical)     | 80mW(5V*16mA)                                 |

Notes: 1.When random texts pattern is running , averagely , at any instance , about 1/2 of pixels will be on.

2. You can to use the display off mode to make long life.

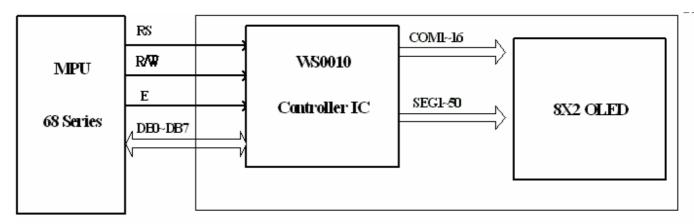

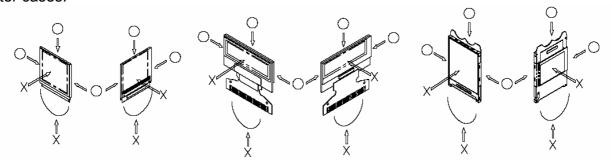

# 7. Counter Drawing & Block Diagram

| PIN NO. | SYMBOL |

|---------|--------|

| 1       | Vss    |

| 2       | Vdd    |

| 3       | NC     |

| 4       | RS     |

| 5       | R/W    |

| 6       | Е      |

| 7       | DB0    |

| 8       | DB1    |

| 9       | DB2    |

| 10      | DB3    |

| 11      | DB4    |

| 12      | DB5    |

| 13      | DB6    |

| 14      | DB7    |

| 15      | NC     |

| 16      | NC     |

|         |        |

The non-specified tolerance of dimension is 9.3 mm.

| Address Format         | DB7 | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|------------------------|-----|------|------|------|------|------|------|------|

| CA (Character Address) | 1   | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

| 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8          |

|------------|------------|------------|------------|------------|------------|------------|------------|

| CA10000000 | CA10000001 | CA10000010 | CA10000011 | CA10000100 | CA10000101 | CA10100110 | CA10100111 |

| CA11000000 | CA11000001 | CA11000010 | CA11000011 | CA11000100 | CA11000101 | CA11000110 | CA11000111 |

# 8. Function Description

### **REGISTERS**

IC provides two types of 8-bit registers, namely: Instruction Register (IR) and Data Register (DR). The register is selected using the RS Pin. When the RS pin is set to "0", the Instruction Register Type is selected. When RS pin is set to "1", the Data Register Type is selected. Please refer to the table below.

| RS | R/WB | Operation                                                           |

|----|------|---------------------------------------------------------------------|

| 0  | 0    | Instruction register write as an internal operation.                |

| 0  | 1    | Read busy flag (DB7) and address counter (DB0 to DB6)               |

| 1  | 0    | Data register write as an internal operation (DR to DDRAM or CGRAM) |

| 1  | 1    | Data register read as an internal operation (DDRAM or CGRAM to DR)  |

### **INSTRUCTION REGISTER (IR)**

The Instruction Register is used to store the instruction code (i.e. Display Clear, Cursor Home and others), Display Data RAM (DDRAM) Address, and the Character Generator RAM (CGRAM) Address. Instruction register can only be written from the MPU.

### **DATA REGISTER (DR)**

The Data Register is used as a temporary storage for data that are going to be written into the DDRAM or CGRAM as well as those data that are going to be read from the DDRAM or CGRAM.

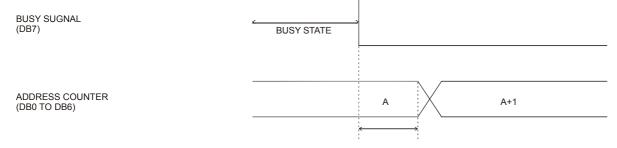

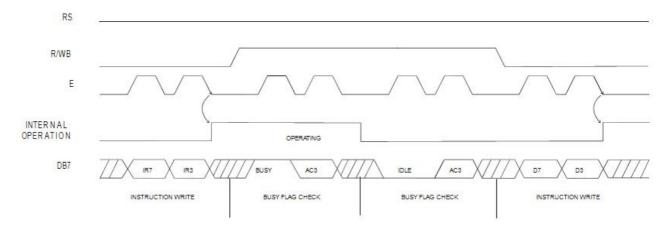

### BUSY FLAG (BF)

The Busy Flag is used to determine whether IC is idle or internally operating. When IC is performing some internal operations, the Busy Flag is set to "1". Under this condition, the no other instruction will not be accepted. When RS Pin is set to "0" and R/WB Pin is set to "1", the Busy Flag will be outputted to the DB7 pin.

When IC is idle or has completed its previous internal operation, the Busy Flag is set to "0". The next instruction can now be processed or executed.

### ADDRESS COUNTER (AC)

The address counter is used to assign the Display Data RAM (DDRAM) Address and the Character Generator RAM (CGRAM) Address. When Address information is written into the Instruction Register (IR), this Address information is sent from the Instruction Register to the Address Counter. At the same time, the nature of the Address (either CGRAM or DDRAM) is determined by the instruction. After writing into or reading from the DDRAM or CGRAM, the Address Counter is automatically increased or decreased by 1 (for Write or Read Function). It must be noted that when the RS pin is set to "0" and R/WB is set to "1", the contents of the Address Counter are outputted to the pins -- DB0 to DB6.

### **DISPLAY DATA RAM (DDRAM)**

The Display Data RAM (DDRAM) is used to store the Display Data which is represented as 8-bit character code. The Display Data RAM supports an extended capacity of 128 x 8-bits or 128 characters.

The Display Data RAM Address (ADD) is set in the Address Counter as a hexadecimal.

|                       | High Ord | ler Bits |     | Low Order Bits |     |     |     |  |  |

|-----------------------|----------|----------|-----|----------------|-----|-----|-----|--|--|

| Address Counter (hex) | AC6      | AC5      | AC4 | AC3            | AC2 | AC1 | AC0 |  |  |

An example of a DDRAM Address=39 is given below.

| DDRAM Address: 39 |                             |  |  |  |  |  |  |  |  |  |

|-------------------|-----------------------------|--|--|--|--|--|--|--|--|--|

| AC6               | AC6 AC5 AC4 AC3 AC2 AC1 AC0 |  |  |  |  |  |  |  |  |  |

| 0 1 1 1 0 0 1     |                             |  |  |  |  |  |  |  |  |  |

### 1-LINE DISPLAY (N=0)

When the number of characters displayed is less than 128, the first character is displayed at the head position. The relationship between the DDRAM Address and position on the OLED Panel is shown below.

| Display Position (digit)    | 1  | 2  | 3  | 4  | <br>126 | 127 | 128 |

|-----------------------------|----|----|----|----|---------|-----|-----|

| DDRAM address (hexadecimal) | 00 | 01 | 02 | 03 | <br>7D  | 7E  | 7F  |

For example, when only 8 characters are displayed in one Display Line, the relationship between the DDRAM Address and position on the OLED Panel is shown below.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|------------------|----|----|----|----|----|----|----|----|

| DDRAM address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

|                  |    |    |    |    |    |    |    |    |

| Shift left       | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

|                  |    |    |    |    |    |    |    |    |

| Shift right      | 7F | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

## 2-LINE DISPLAY (N=1)

Case 1: The Number of Characters displayed is less than 64 x 2 lines

When the number of characters displayed is less than 64 x 2 lines, then the first character of the first and second lines are displayed starting from the head. It is important to note that every line reserve 64 x8bits DDRAM space. 1<sup>st</sup> line is 00 to 3F,second line is 40 to 7F.Please refer the figure below.

| Display Position | 1  |    | 3  | 4  | <br>61 | 62 | 63 | 64 |

|------------------|----|----|----|----|--------|----|----|----|

|                  | 00 | 01 | 02 | 03 | <br>3C | 3D | 3E | 3F |

| (hexadecimal)    | 40 | 41 | 42 | 43 | <br>7C | 7D | 7E | 7F |

To illustrate, for 2-line x 20 characters display, the relationship between the DDRAM address and position of the OLED panel is shown below.

| Display Position | 1  | 2  | 3  | 4  | <br>18 | 19 | 20 |

|------------------|----|----|----|----|--------|----|----|

| DDRAM address    | 00 | 01 | 02 | 03 | <br>11 | 12 | 13 |

| (hexadecimal)    | 40 | 41 | 42 | 43 | <br>51 | 52 | 53 |

|                  |    |    | l  |    |        |    |    |

|                  | 01 | 02 | 03 | 04 | <br>12 | 13 | 14 |

| Shift left       | 41 | 42 | 43 | 44 | <br>52 | 53 | 54 |

|                  |    |    |    |    |        |    |    |

| Shift right      | 3F | 00 | 01 | 02 | <br>10 | 11 | 12 |

| Offine right     | 7F | 40 | 41 | 42 | <br>50 | 51 | 52 |

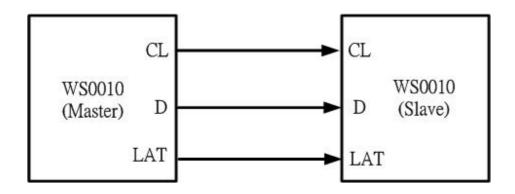

Case 2: 40-Character x 2 Lines Display IC(Master) can be extended to display 40 characters x 2 lines by cascade the other IC(Slave). When there is a Display Shift operation, the DDRAM Address is also shifted. Please refer to the example below.

| Display<br>Position | 1     | 2     | 3   | 4     | 5  | 6  | 7  | 8  | 9   | 10   | 11                 | ••••  | 37  | 38 | 39 | 40 |

|---------------------|-------|-------|-----|-------|----|----|----|----|-----|------|--------------------|-------|-----|----|----|----|

|                     | 00    | 01    | 02  | 03    | 04 | 05 | 06 | 07 | 80  | 09   | 0A                 | ••••  | 24  | 25 | 26 | 27 |

| DDRAM address       | 40    | 41    | 42  | 43    | 44 | 45 | 46 | 47 | 48  | 49   | 4A                 | ••••  | 64  | 65 | 66 | 67 |

|                     | IC di | splay | (Ma | ster) |    |    | •  | •  | Cas | cade | 2 <sup>nd</sup> IC | (Slav | ve) |    | •  | •  |

|                     |       |       |     |       |    |    |    |    |     |      |                    |       |     |    |    |    |

| Shift left          | 01    | 02    | 03  | 04    | 05 | 06 | 07 | 80 | 09  | 0A   | 0B                 | ••••  | 25  | 26 | 27 | 28 |

| Still left          | 41    | 42    | 43  | 44    | 45 | 46 | 47 | 48 | 49  | 4A   | 4B                 | ••••  | 65  | 66 | 67 | 68 |

|                     |       | •     |     |       |    |    | •  | •  |     |      |                    | •     |     | •  | •  |    |

| Shift right         | 3F    | 00    | 01  | 02    | 03 | 04 | 05 | 06 | 07  | 80   | 09                 | ••••  | 23  | 24 | 25 | 26 |

| Shiit right         | 7F    | 40    | 41  | 42    | 43 | 44 | 45 | 46 | 47  | 48   | 49                 | ••••  | 63  | 64 | 65 | 66 |

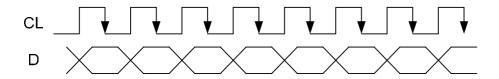

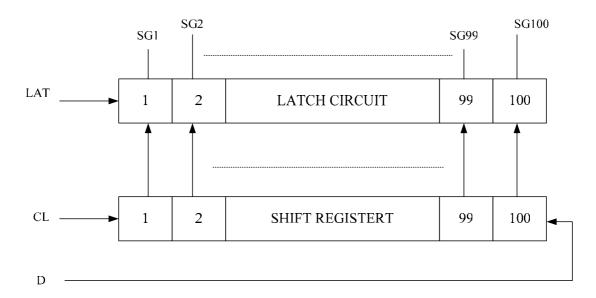

### SLAVE MODE DATA INPUT

When IC is under slave mode, display data is send from the other IC(master). The input data "D" is shifted at the falling edge of CL

| M/S | Mode   | D      | CL     | LAT    |

|-----|--------|--------|--------|--------|

| Н   | Master | Output | Output | Output |

| L   | Slave  | Input  | Input  | Input  |

### BIDIRECTIONAL SHIFT REGISTER BLOCK

This block shifts the serial data at the falling edge of CL. When SHL is set "H", the data input from D is shifted from bit100 to bit1 (When IC is "master" mode, D is output; When IC is "slave" mode, D is input). When SHL is set "L", the data input is shifted from bit1 to bit100.

#### Condition 1: SHL="H"

#### Condition 2 : SHL="L

### CHARACTER GENERATOR ROM (CGROM)

The Character Generator ROM (CGROM) is used to generate either 5 x 8 dots or 5 x 10 dots character patterns from 8-bit character codes.IC build in three set of font tables as "Western European", "English Japanese" and "English Russian". User can use software to select suitable font table (**Default** "English Japanese").

## CHARACTER GENERATOR RAM (CGRAM)

The Character Generator RAM (CGRAM) is used to generate either  $5 \times 8$  dot or  $5 \times 10$  dot character patterns. It can generate eight  $5 \times 8$  dot character patterns or four  $5 \times 10$  dot character patterns. The character patterns generated by the CGRAM can be rewritten. User-defined character patterns for the CGRAM are supported.

# RELATIONSHIP BETWEEN CGRAM ADDRESS, DDRAM CHARACTER CODE AND CGRAM CHARACTER PATTERNS (FOR 5 X 8 DOT CHARACTER PATTERN)

|     |    |   | r C |   | s |    |   |     |    |   |     |    |   |   |     |   |   | r Pa |   | rns | 5  |   |                     |

|-----|----|---|-----|---|---|----|---|-----|----|---|-----|----|---|---|-----|---|---|------|---|-----|----|---|---------------------|

| (D  |    | _ | Dat |   | r |    | , |     |    |   | Ado | _  | _ |   | _   | _ | - | Da   |   |     |    | _ |                     |

| 7   | 6  | 5 | 4   | 3 | 2 | 1  | 0 | _   |    | 3 | 2   | 1  | 0 |   |     | 6 | 5 | 4    | 3 | 2   | 1  | 0 |                     |

| Ηiς | gh |   |     |   |   | Lo | W | Ηiς | gh |   |     | Lo | W |   | Ηiς |   |   |      |   |     | Lo | W |                     |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 0 |   | *   | * | * | 1    | 1 | 1   | 1  | 0 | Character pattern 1 |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 1 |   | *   | * | * | 1    | 0 | 0   | 0  | 1 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 1  | 0 |   | *   | * | * | 1    | 0 | 0   | 0  | 1 |                     |

| 0   | 0  | 0 | 0   | * | 0 | 0  | 0 | 0   | 0  | 0 | 0   | 1  | 1 |   | *   | * | * | 1    | 1 | 1   | 1  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 0 |   | *   | * | * | 1    | 0 | 1   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 1 |   | *   | * | * | 1    | 0 | 0   | 1  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 0 |   | *   | * | * | 1    | 0 | 0   | 0  | 1 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 1 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 | Cursor Position     |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 0 |   | *   | * | * | 1    | 0 | 0   | 0  | 1 | Character pattern 2 |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 1 | 1 | *   | * | * | 0    | 1 | 0   | 1  | 0 | ·                   |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 1  | 0 | 1 | *   | * | * | 1    | 1 | 1   | 1  | 1 |                     |

| 0   | 0  | 0 | 0   | * | 0 | 0  | 1 | 0   | 0  | 1 | 0   | 1  | 1 | 1 | *   | * | * | 0    | 0 | 1   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 0 | 1 | *   | * | * | 1    | 1 | 1   | 1  | 1 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 1 |   | *   | * | * | 0    | 0 | 1   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 0 |   | *   | * | * | 0    | 0 | 1   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 1 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 | Cursor position     |

| 0   | 0  | 0 | 0   | * |   |    |   |     |    |   |     | İ  | i |   |     |   |   |      |   |     | i. |   | Character pattern   |

|     |    |   |     |   |   |    |   |     |    |   |     |    |   |   |     |   |   |      |   |     |    |   | 3~7                 |

|     |    |   |     |   |   |    |   |     |    |   |     |    |   |   | *   | * | * |      |   |     |    |   |                     |

|     |    |   |     |   |   |    |   |     |    |   |     |    |   |   |     |   |   |      |   |     |    |   |                     |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 0 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 | Character pattern 8 |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 0  | 1 |   | *   | * | * | 0    | 1 | 0   | 1  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 0   | 1  | 0 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 |                     |

| 0   | 0  | 0 | 0   | * | 1 | 1  | 1 | 1   | 1  | 1 | 0   | 1  | 1 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 0 |   | *   | * | * | 1    | 0 | 0   | 0  | 1 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 0  | 1 |   | *   | * | * | 0    | 1 | 1   | 1  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 0 |   | *   | * | * | 0    | 0 | 1   | 0  | 0 |                     |

|     |    |   |     |   |   |    |   |     |    |   | 1   | 1  | 1 |   | *   | * | * | 0    | 0 | 0   | 0  | 0 | Cursor position     |

#### Notes:

- 1. \* = Not Relevant

- 2. The character pattern row positions correspond to the CGRAM data bits -- 0 to 4, where bit 4 is in the left position.

- 3. Character Code Bits 0 to 2 correspond to the CGRAM Address Bits 3 to 5 (3 bits: 8 types)

- 4. If the CGRAM Data is set to "1", then the selection is displayed. If the CGRAM is set to "0", there no selection is made.

- 5. The CGRAM Address Bits 0 to 2 are used to define the character pattern line position. The 8th line is the cursor position and its display is formed by the logical OR with the cursor. The 8th line CGRAM data bits 0 to 4 must be set to "0". If any of the 8th line CGRAM data bits 0 to 4 is set to "1", the corresponding display location will light up regardless of the cursor position.

- 6. When the Character Code Bits 4 to 7 are set to "0", then the CGRAM Character Pattern is selected. It must be noted that Character Code Bit 3 is not relevant and will not have any effect on the character display. Because of this, the first Character Pattern shown above (R) can be displayed when the Character Code is 00H or 08H.

# RELATIONSHIP BETWEEN CGRAM ADDRESS, DDRAM CHARACTER CODE AND CGRAM CHARACTER PATTERNS (FOR 5 X10 DOT CHARACTER PATTERN)

| Ch  |    |   | r C |   |    |    |   |     |      |               |     |     | 1- | <u> </u> |    |    |   |    | atte |           |    | */ * | CIER PATTERN)         |

|-----|----|---|-----|---|----|----|---|-----|------|---------------|-----|-----|----|----------|----|----|---|----|------|-----------|----|------|-----------------------|

| I . |    |   | Da  |   |    |    |   | CG  | aR A | M.            | Add | dre | ss |          |    |    |   | Da |      | , I I I I | 3  |      |                       |

| 7   | 6  | 5 | 1   | 3 | 2  | 1  | 0 | _   | 4    |               | 2   | 1   | 0  |          | 7  | 6  | 5 | 4  |      | 2         | 1  | 0    |                       |

| Hi  | gh |   |     |   |    | Lc | W | Hiç | gh   |               |     | Lo  | W  |          | Hi | gh |   |    |      |           | Lo | W    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 0   | 0  |          | *  | *  | * | 0  | 0    | 1         | 0  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 0   | 1  |          | *  | *  | * | 0  | 1    | 1         | 1  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 1   | 0  |          | *  | *  | * | 1  | 0    | 1         | 0  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 1   | 1  |          | *  | *  | * | 1  | 0    | 1         | 0  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 0   | 0  |          | *  | *  | * | 0  | 1    | 1         | 0  | 0    | Character pattern 1   |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 0   | 1  |          | *  | *  | * | 0  | 0    | 1         | 1  | 0    | Character pattern 1   |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 1   | 0  |          | *  | *  | * | 0  | 0    | 1         | 0  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 1   | 1  |          | *  | *  | * | 1  | 0    | 1         | 0  | 1    |                       |

| 0   | 0  | 0 | 0   | * | 0  | 0  | * | 0   | 0    | 1             | 0   | 0   | 0  |          | *  | *  | * | 0  | 1    | 1         | 1  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 0   | 0   | 1  |          | *  | *  | * | 0  | 0    | 1         | 0  | 0    | Oursen Desition       |

|     |    |   |     |   |    |    |   |     |      | 1             | 0   | 1   | 0  |          | *  | *  | * | *  | *    | *         | *  | *    | Cursor Position       |

|     |    |   |     |   |    |    |   |     |      | <u>1</u><br>1 | 0   | 0   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 0   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 1   | 0  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 1   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    | L  |   |     |      | Ė             | Ŀ   | Ľ   | Ŀ  |          |    |    |   |    |      |           |    | L    | Character pattern     |

|     |    |   |     |   | ļ. | Ĺ  |   | Ĺ   | Ĺ    | Ĺ             |     |     |    |          |    |    |   | į. |      | Ŀ         | Ĺ  | Ŀ    | 2~3                   |

| 0   | 0  | 0 | 0   | * |    |    | * |     |      |               |     |     |    |          | *  | *  | * | -  | -    |           |    |      |                       |

|     |    |   |     |   |    |    |   |     |      |               |     |     |    |          |    |    |   |    |      |           |    |      |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 0   | 0  |          | *  | *  | * | 1  | 0    | 1         | 0  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 0   | 1  |          | *  | *  | * | 1  | 1    | 1         | 1  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 1   | 0  |          | *  | *  | * | 1  | 1    | 1         | 1  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 0   | 1   | 1  |          | *  | *  | * | 1  | 1    | 1         | 1  | 1    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 0   | 0  |          | *  | *  | * | 0  | 1    | 1         | 1  | 0    | Character pattern 4   |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 0   | 1  | -        | *  | *  | * | 0  | 0    | 1         | 0  | 0    | - Character pattern 1 |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 1   | 0  |          | *  | *  | * | 0  | 0    | 1         | 0  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 0             | 1   | 1   | 1  |          | *  | *  | * | 1  | 0    | 1         | 0  | 1    |                       |

| 0   | 0  | 0 | 0   | * | 1  | 1  | * | 1   | 1    | <u>1</u><br>1 | 0   | 0   | 0  |          | *  | *  | * | 0  | 0    | 1         | 0  | 0    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 0   | 1   | 0  |          | *  | *  | * | *  | *    | *         | *  | *    | Cursor Position       |

|     |    |   |     |   |    |    |   |     |      | 1             | 0   | 1   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    | Outsot Fosition       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 0   | 0  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 0   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 1   | 0  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

|     |    |   |     |   |    |    |   |     |      | 1             | 1   | 1   | 1  |          | *  | *  | * | *  | *    | *         | *  | *    |                       |

#### Notes:

- 1. \* = Not Relevant

- 2. The character pattern row positions correspond to the CGRAM data bits -- 0 to 4, where bit 4 is in the left position.

- 3. Character Code Bits 1 and 2 correspond to the CGRAM Address Bits -- 4 and 5 respectively (2 bits : 4 types)

- 4. If the CGRAM Data is set to "1", then the selection is displayed. If the CGRAM is set to "0", there no selection is made.

- 5. The CGRAM Address Bits 0 to 3 are used to define the character pattern line position. The 11th line is the cursor position and its display is formed by the logical OR with the cursor. The 11th line CGRAM data bits 0 to 4 must be set to "0". If any of the 11th line CGRAM data bits 0 to 4 is set to "1", the corresponding display location will light up regardless of the cursor position.

- 6. When the Character Code Bits 4 to 7 are set to "0", then the CGRAM Character Pattern is selected. It must be noted that Character Code Bit -- 0 and 3 are not relevant and will not have any effect on the character display. Because of this, the Character Pattern shown above (\$) can be displayed when the Character Code is 00H, 01H, 08H or 09H.

#### TIMING GENERATION CIRCUIT

The timing signals for the internal circuit operations (i.e. DDRAM, CGRAM, and CGROM) are generated by the Timing Generation Circuit. The timing signals for the MPU internal operation and the RAM Read for Display are generated separately in order to prevent one from interfering with the other. This means that, for example, when the data is being written into the DDRAM, there will be no unwanted interference such as flickering in areas other than the display area.

#### **OLED DRIVER CIRCUIT**

IC provides 16 Common Drivers and 100 Segment Driver Outputs. When a character font and the number of lines to be displayed have been selected, the corresponding Common Drivers output the waveform automatically. A non-selection waveform will be outputted by the rest of the Common outputs.

#### CURSOR/BLINK CONTROL CIRCUIT

The cursor or character blinking is generated by the Cursor / Blink Control Circuit. The cursor or the blinking will appear with the digit located at the Display Data RAM (DDRAM) Address Set in the Address Counter (AC).

|                 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

|-----------------|-----|-----|-----|-----|-----|-----|-----|

| Address counter | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

#### **CASE 1: FOR 1-LINE DISPLAY**

Example: When the Address Counter (AC) is set to 0EH, the cursor position is displayed at DDRAM Address 0EH.

| Display position            | 1  | 2  | 3  | 4  | 5  | <br>14 | 15           |         | 19 | 20 |

|-----------------------------|----|----|----|----|----|--------|--------------|---------|----|----|

| DDRAM address (hexadecimal) | 00 | 01 | 02 | 03 | 04 | <br>0D | 0E           |         | 12 | 13 |

|                             |    |    |    |    |    | Cı     | <br>ursor Po | osition |    |    |

#### Notes:

The cursor or blinking appears when the Address Counter (AC) selects the Character Generator RAM (CGRAM). When the AC selects CGRAM Address, then the cursor or the blinking is displayed in a irrelevant and meaningless position.

#### CASE 2: FOR 2-LINE DISPLAY

Example: When the Address Counter (AC) is set to 46H, the cursor position is displayed at DDRAM Address 46H.

| Display position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | <br>19 | 20 |

|------------------|----|----|----|----|----|----|----|----|--------|----|

| DDRAM address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | <br>09 | 13 |

| (hexadecimal)    | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | <br>49 | 53 |

#### **Cursor Position**

#### Notes:

The cursor or blinking appears when the Address Counter (AC) selects the Character Generator RAM (CGRAM). When the AC selects CGRAM Address, then the cursor or the blinking is displayed in an irrelevant and meaningless position.

### CHARACTER MODE ADDRESSING

WIN0010 provides two kind of character mode. User can fill in 128 characters data (N=0, one line) or 64 characters data per line (N=1, two line) in embedded RAM to display graphic. Character mode address can be controlled by DDRAM address instruction.

| Address Forr     | nat     | DB7 | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|------------------|---------|-----|------|------|------|------|------|------|------|

| CA (Character Ad | ldress) | 1   | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

### (1)1-Line condition (N=0)

| 1           | 2           | 3           | 4           | <br> | 125         | 126         | 127         | 128         |

|-------------|-------------|-------------|-------------|------|-------------|-------------|-------------|-------------|

| CA=10000000 | CA=10000001 | CA=10000010 | CA=10000011 |      | CA=11111100 | CA=11111101 | CA=11111110 | CA=11111111 |

### (2)2-Line condition (N=1)

| 1           | 2           | 3           | 4           | <br> | 61          | 62          | 63          | 64          |

|-------------|-------------|-------------|-------------|------|-------------|-------------|-------------|-------------|

| CA=10000000 | CA=10000001 | CA=10000010 | CA=10000011 |      | CA=10111100 | CA=10111101 | CA=10111110 | CA=10111111 |

| CA=11000000 | CA=11000001 | CA=11000010 | CA=11000011 |      | CA=11111100 | CA=11111101 | CA=11111110 | CA=11111111 |

### **GRAPHIC MODE ADDRESSING**

WIN0010 provides not only character mode but also graphic mode. User can fill in 100x16 data in embedded RAM to display graphic. Graphic mode addressing is different from character mode.

Use DDRAM address instruction to set X-axis address of Graphic mode and CGRAM address instruction to set Y-axis of Graphic mode.

| Address Format               | DB7 | DB6  | DB5  | DB4  | DB3  | DB2  | DB1  | DB0  |

|------------------------------|-----|------|------|------|------|------|------|------|

| GXA (Graphic X-axis Address) | 1   | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

| GYA (Graphic Y-axis Address) | 0   | 1    | 0    | 0    | 0    | 0    | 0    | CGA0 |

|        | 1                            | 2                            | 3                            | 4                            |                                              | <br>97                       | 98                           | 99                           | 100                          |

|--------|------------------------------|------------------------------|------------------------------|------------------------------|----------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| CGA0=0 | GXA=10000000<br>GYA=01000000 | GXA=10000001<br>GYA=01000000 | GXA=10000010<br>GYA=01000000 | GXA=10000011<br>GYA=01000000 | D0 D1 D2 D3 D4 D5 D6 D7                      | GXA=11100000<br>GYA=01000000 | GXA=11100001<br>GYA=01000000 | GXA=11100010<br>GYA=01000000 | GXA=11100011<br>GYA=01000000 |

| CGA0=1 | GXA=10000000<br>GYA=01000001 | GXA=10000001<br>GYA=01000001 | GXA=10000010<br>GYA=01000001 | GXA=10000011<br>GYA=01000001 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | GXA=11100000<br>GYA=01000001 | GXA=11100001<br>GYA=01000001 | GXA=11100010<br>GYA=01000001 | GXA=11100011<br>GYA=01000001 |

# **9.Character Generator ROM Pattern**

CHARACTER GENERATOR ROM (CGROM)

WIN0010 provides three set of character font. Character font can be selected by programming FT.

ENGLISH\_JAPANESE CHARACTER FONT TABLE(default FT[1:0]= 00)

| ENGLISH                  | _JA               | PAN  | ESE  | CH   | AKA  | CIE  | K F  | JNI  | IAD  | SLE(C | аета | uit F | 1[1: | υj= ι | JU)  |      |

|--------------------------|-------------------|------|------|------|------|------|------|------|------|-------|------|-------|------|-------|------|------|

| Upper 4bit<br>Lower 4bit | ш                 | LLLH | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH  | HLHL | HLHH  | HHLL | HHLH  | HHHL | нннн |

| ш                        | CG<br>RAM<br>(1)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| ш                        | CG<br>RAM<br>(2)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LLHL                     | CG<br>RAM<br>(3)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LLHH                     | CG<br>RAM<br>(4)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LHLL                     | CG<br>RAM<br>(5)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LHLH                     | CG<br>RAM<br>(6)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LHHL                     | CG<br>RAM<br>(7)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| LHHH                     | CG<br>RAM<br>(8)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HLLL                     | CG<br>RAM<br>(9)  |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HLLH                     | CG<br>RAM<br>(10) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HLHL                     | CG<br>RAM<br>(11) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HLHH                     | CG<br>RAM<br>(12) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HHLL                     | CG<br>RAM<br>(13) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HHLH                     | CG<br>RAM<br>(14) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| HHHL                     | CG<br>RAM<br>(15) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

| ннин                     | CG<br>RAM<br>(16) |      |      |      |      |      |      |      |      |       |      |       |      |       |      |      |

# WESTERN EUROPEAN CHARACTER FONT TABLE | (FT[1:0]=01)

|                          | ·                 |      |      |      |      | <u> </u> |      |      | 17 \ |      | ( - 1 | -נט.ו | 01)  |         |      |      |

|--------------------------|-------------------|------|------|------|------|----------|------|------|------|------|-------|-------|------|---------|------|------|

| Upper 4hit<br>Lower 4hit | ш                 | LLLH | LLHL | LLHH | LHLL | LHLH     | LHHL | LHHH | HLLL | HLLH | HLHL  | HLHH  | HHLL | HHLH    | HHHL | нннн |

| ш                        | CG<br>RAM<br>(1)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| ш                        | CG<br>RAM<br>(2)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LLHL                     | CG<br>RAM<br>(3)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LLHH                     | CG<br>RAM<br>(4)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LHLL                     | CG<br>RAM<br>(5)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LHLH                     | CG<br>RAM<br>(6)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LHHL                     | CG<br>RAM<br>(7)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| LHHH                     | CG<br>RAM<br>(8)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HLLL                     | CG<br>RAM<br>(9)  |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HLLH                     | CG<br>RAM<br>(10) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HLHL                     | CG<br>RAM<br>(11) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HLHH                     | CG<br>RAM<br>(12) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HHLL                     | CG<br>RAM<br>(13) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HHLH                     | CG<br>RAM<br>(14) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

| HHHL                     | CG<br>RAM<br>(15) |      |      |      |      |          |      |      |      |      |       |       |      | <b></b> |      |      |

| нннн                     | CG<br>RAM<br>(16) |      |      |      |      |          |      |      |      |      |       |       |      |         |      |      |

**ENGLISH\_RUSSIAN CHARACTER FONT TABLE(FT[1:0]=10)**

| ENGLION.      |                   | <u> </u> | III C |      | ACI  | <u> </u> |      |      |      | <u> </u> | -LO. | 10)  |      |      |      |      |

|---------------|-------------------|----------|-------|------|------|----------|------|------|------|----------|------|------|------|------|------|------|

| Upper<br>4bit | ш                 | LLLH     | LLHL  | LLHH | LHLL | LHLH     | LHHL | LHHH | HLLL | HLLH     | HLHL | HLHH | HHLL | HHLH | HHHL | нннн |

| ш             | CG<br>RAM<br>(1)  | H        |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| ш             | CG<br>RAM<br>(2)  |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| LLHL          | CG<br>RAM<br>(3)  | Ħ        |       |      |      |          |      |      |      |          |      |      |      |      | Ш    |      |

| LLHH          | CG<br>RAM<br>(4)  | Ħ        |       |      |      |          |      |      |      |          | H    |      |      |      |      |      |

| LHLL          | CG<br>RAM<br>(5)  | H        |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| LHLH          | CG<br>RAM<br>(6)  | Ħ        |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| LHHL          | CG<br>RAM<br>(7)  | Æ        |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| LHHH          | CG<br>RAM<br>(8)  |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HLLL          | CG<br>RAM<br>(9)  |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HLLH          | CG<br>RAM<br>(10) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HLHL          | CG<br>RAM<br>(11) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HLHH          | CG<br>RAM<br>(12) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HHLL          | CG<br>RAM<br>(18) |          |       |      |      |          |      |      |      |          | Ш    |      |      |      |      |      |

| ннгн          | CG<br>RAM<br>(14) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| HHHL          | CG<br>RAM<br>(15) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

| нннн          | CG<br>RAM<br>(16) |          |       |      |      |          |      |      |      |          |      |      |      |      |      |      |

# WESTERN EUROPEAN CHARACTER FONT TABLE II (FT[1:0]=1

|                          |                   |      |      |      | 17 (1 (7 |      | <del></del> | <u> </u> |      |      | <u>, (, , , , , , , , , , , , , , , , , , </u> | <u>[1.0</u> | <u> </u> |      |      |      |

|--------------------------|-------------------|------|------|------|----------|------|-------------|----------|------|------|------------------------------------------------|-------------|----------|------|------|------|

| Upper 4bit<br>Lower 4bit | ш                 | LLLH | LLHL | LLHH | LHLL     | LHLH | LHHL        | LHHH     | HLLL | HLLH | HLHL                                           | HLHH        | HHLL     | HHLH | HHHL | нннн |

| ш                        | CG<br>RAM<br>(1)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| ш                        | CG<br>RAM<br>(2)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| LLHL                     | CG<br>RAM<br>(3)  |      |      |      |          | R    |             |          |      |      |                                                |             |          |      |      |      |

| LLHH                     | CG<br>RAM<br>(4)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| LHLL                     | CG<br>RAM<br>(5)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| LHLH                     | CG<br>RAM<br>(6)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| LHHL                     | CG<br>RAM<br>(7)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| LHHH                     | CG<br>RAM<br>(8)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HLLL                     | CG<br>RAM<br>(9)  |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HLLH                     | CG<br>RAM<br>(10) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HLHL                     | CG<br>RAM<br>(11) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HLHH                     | CG<br>RAM<br>(12) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HHLL                     | CG<br>RAM<br>(13) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| HHLH                     | CG<br>RAM<br>(14) |      |      |      |          |      |             |          |      |      |                                                |             |          | W    |      |      |

| HHHL                     | CG<br>RAM<br>(15) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

| нннн                     | CG<br>RAM<br>(16) |      |      |      |          |      |             |          |      |      |                                                |             |          |      |      |      |

# 10. Instruction Table

| Instruction                                 | Code |      |         |            |     | Description | Max.<br>Execution<br>Time when |     |     |     |                                                                                                                                                                                     |                         |

|---------------------------------------------|------|------|---------|------------|-----|-------------|--------------------------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                             | RS   | R/WB | DB7     | DB6        | DB5 | DB4         | DB3                            | DB2 | DB1 | DB0 |                                                                                                                                                                                     | fsp or fosc =<br>250KHz |

| Clear Display                               | 0    | 0    | 0       | 0          | 0   | 0           | 0                              | 0   | 0   | 1   | Clears entire display.<br>Sets DDRAM Address 0 into the<br>Address Counter                                                                                                          | 6.2ms                   |

| Return Home                                 | 0    | 0    | 0       | 0          | 0   | 0           | 0                              | 0   | 1   | 0   | Sets DDRAM Address 0 into the Address Counter. Returns shifted display to original position. DDRAM contents remain unchanged. (DB0 is test pin. User should set DB0=0 all the time) | 0                       |

| Entry Mode<br>Set                           | 0    | 0    | 0       | 0          | 0   | 0           | 0                              | 1   | I/D | S   | Sets cursor move direction and specifies display shift. (These operations are performed during data write and read.)                                                                | 0                       |

| Display<br>ON/OFF<br>Control                | 0    | 0    | 0       | 0          | 0   | 0           | 1                              | D   | С   | В   | Sets entire Display (D) ON/OFF.<br>Sets Cursor (C) ON/OFF.<br>Sets Blinking (B) of Cursor<br>Position Character.                                                                    | 0                       |

| Cursor/<br>Display Shift/<br>Mode/ Pwr      | 0    | 0    | 0       | 0          | 0   | 1           | S/C                            | R/L | 0   | 0   | Moves cursor & shifts display without changing DDRAM contents.  Sets Graphic/Character Mode                                                                                         | 0                       |

|                                             |      |      |         |            |     |             | G/C                            | PWR | 1   | 1   | Sets internal power on/off                                                                                                                                                          |                         |

| Function Set                                | 0    | 0    | 0       | 0          | 1   | DL          | N                              | F   | FT1 | FT0 | Sets interface data length (DL). Sets number of display lines (N). Sets Character Font (F). Sets Font Table (FT)                                                                    | 0                       |

| et CGRAM<br>Address                         | 0    | 0    | 0       | 1          | ACG | ACG         | ACG                            | ACG | ACG | ACG | Sets CGRAM Address. CGRAM data is sent and received after this setting.                                                                                                             | 0                       |

| et DDRAM<br>Address                         | 0    | 0    | 1       | ADD        | ADD | ADD         | ADD                            | ADD | ADD | ADD | Sets DDRAM Address. The DDRAM data Is sent and received after this setting.                                                                                                         | 0                       |

| ead Busy<br>Flag &<br>Address               | 0    | 1    | BF      | AC         | AC  | AC          | AC                             | AC  | AC  | AC  | Reads Busy Flag (BF) indicating<br>that internal operation is being<br>performed.<br>Reads Address Counter<br>contents.                                                             | 0                       |

| Write data<br>into the<br>CGRAM or<br>DDRAM | 1    | 0    | Write D | Write Data |     |             |                                |     |     |     | Writes data into the CGRAM or DDRAM                                                                                                                                                 | 0                       |

| Read Data<br>from the<br>CGRAM or<br>DDRAM  | 1    | 1    | Read [  | Oata       |     |             |                                |     |     |     | Read data from the CGRAM or DDRAM                                                                                                                                                   | 0                       |

# 11. Timing Characteristics

### **AC CHARACTERISTICS**

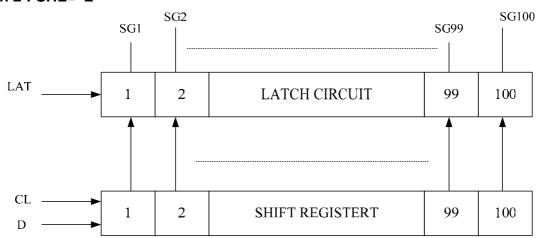

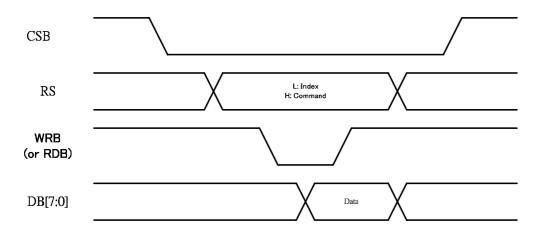

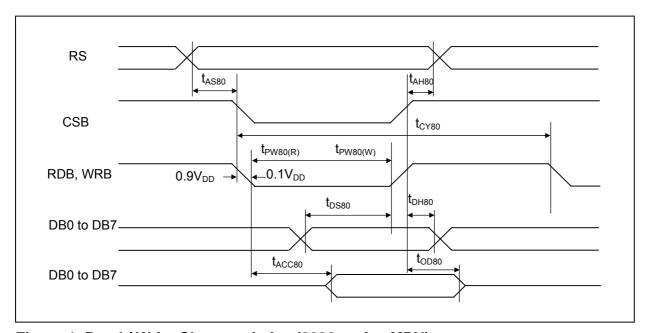

## Read / Write Characteristics (8080-series MPU)

Figure 1. Read / Write Characteristics (8080-series MPU)

$VDD = 3.0 \text{ to } 5.3V, Ta = 25^{\circ}C)$

| Item                                    | Signal | Symbol            | Min.     | Тур. | Max.     | Unit | Remark        |

|-----------------------------------------|--------|-------------------|----------|------|----------|------|---------------|

| Address setup time<br>Address hold time | RS     | tas80<br>tah80    | 20<br>0  | -    | -        | ns   |               |

| System cycle time                       |        | tcy80             | 500      | -    | -        | ns   |               |

| Pulse width (WRB)                       | RW_WRB | tpw80(W)          | 250      | -    | -        | ns   |               |

| Pulse width (RDB)                       | E_RDB  | t <b>PW80</b> (R) | 250      | -    | -        | ns   |               |

| Data setup time<br>Data hold time       | DB7    | tDS80<br>tDH80    | 40<br>20 | -    | -        | ns   |               |

| Read access time Output disable time    | DB0    | tACC80<br>tod80   | -<br>10  | -    | 180<br>- | ns   | CL =<br>100pF |

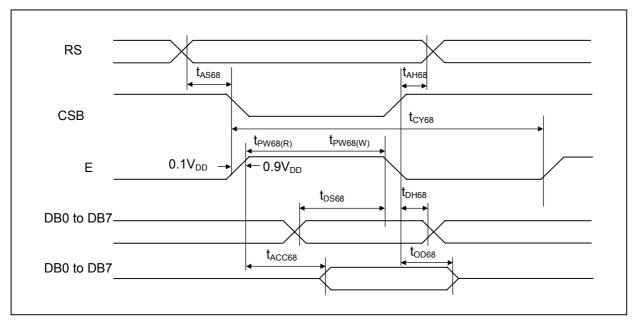

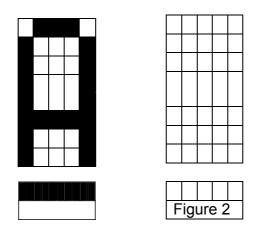

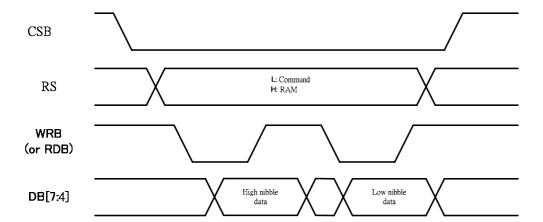

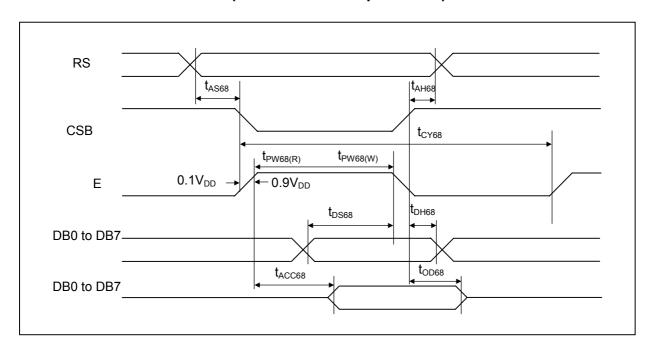

## Read / Write Characteristics (6800-series Microprocessor)

Figure 2. Read / Write Characteristics (6800-series MPU)

(VDD = 3.0 to 5.3V, Ta =  $25^{\circ}$ C)

| Item                                    | Signal    | Symbol            | Min.     | Тур. | Max.     | Unit | Remark        |

|-----------------------------------------|-----------|-------------------|----------|------|----------|------|---------------|

| Address setup time<br>Address hold time | RS        | tas68<br>taн68    | 20<br>0  | -    | -        | ns   |               |

| System cycle time                       |           | tcY68             | 500      | -    | _        | ns   |               |

| Pulse width (E)                         | E_RDB     | tPW68(W)          | 250      | -    | -        | ns   |               |

| Pulse width (E)                         | E_RDB     | t <b>PW68</b> (R) | 250      | -    | -        | ns   |               |

| Data setup time<br>Data hold time       | DB7       | tDS68<br>tDH68    | 40<br>20 | -    | -        | ns   |               |

| Read access time Output disable time    | to<br>DB0 | tacc68<br>tod68   | -<br>10  | -    | 180<br>- | ns   | CL =<br>100pF |

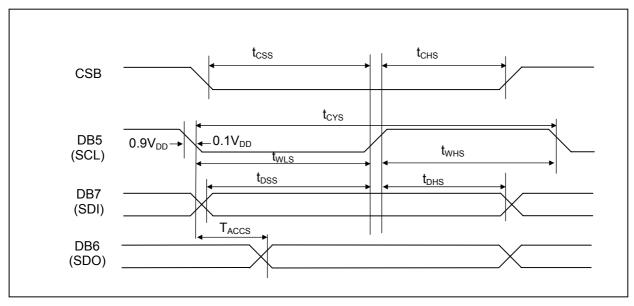

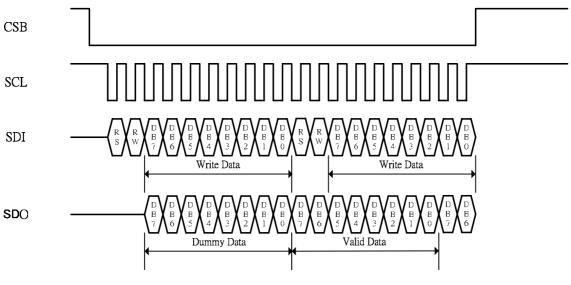

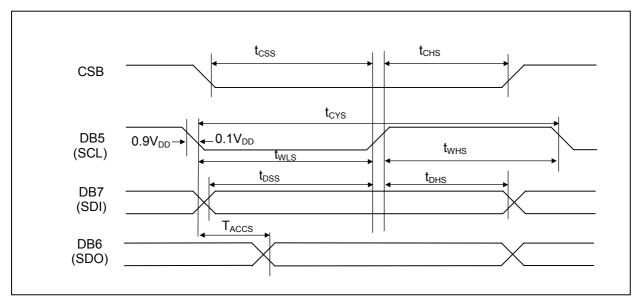

### **Serial Interface Characteristics**

Figure 3. Serial Interface Characteristics

## (VDD = 3.0 to 5.3V, Ta = $25^{\circ}$ C)

| Item                | Signal       | Symbol | Min. | Тур. | Max. | Unit | Remark |  |  |  |  |

|---------------------|--------------|--------|------|------|------|------|--------|--|--|--|--|

| Serial clock cycle  | DDE          | tcys   | 300  | -    | -    |      |        |  |  |  |  |

| SCL low pulse width | (SCL)        | twns   | 100  | -    | -    | ns   |        |  |  |  |  |

| SCL low pulse width | (SCL)        | twLs   | 100  | -    | -    |      |        |  |  |  |  |

| CSB setup time      | CSB          | tcss   | 150  | -    | -    | 20   |        |  |  |  |  |

| CSB hold time       | CSB          | tchs   | 150  | -    | -    | ns   |        |  |  |  |  |

| Data setup time     | DB7          | toss   | 100  | -    | -    | no   |        |  |  |  |  |

| Data hold time      | (SDI)        | tDHS   | 100  | -    | -    | ns   |        |  |  |  |  |

| Read access time    | DB6<br>(SDO) | taccS  | -    | -    | 80   | ns   |        |  |  |  |  |

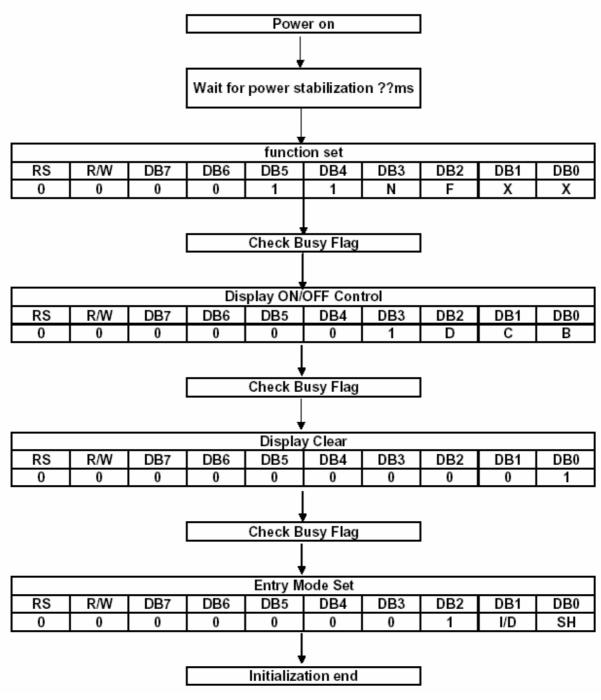

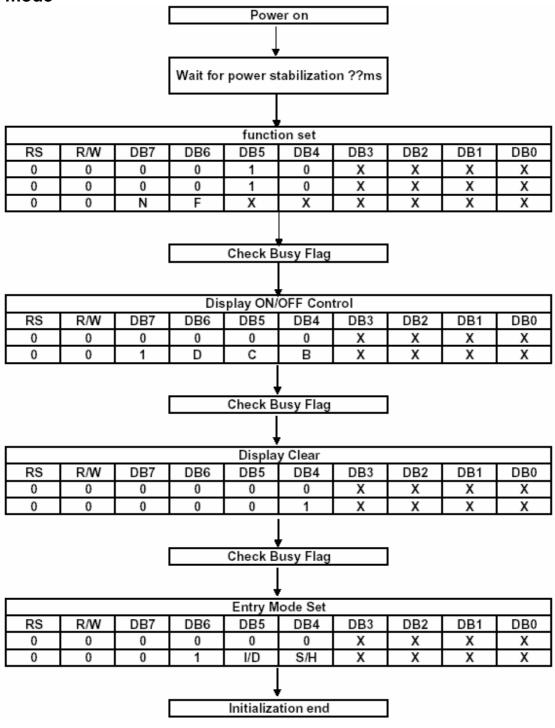

# 12. Initializing of OLED Module

## (1)8-bit mode

# (2)4-bit mode

#### **INSTRUCTIONS**

WIN0010's Instruction Register (IR) and Data Register (DR) are the only registers that can be controlled by the MPU. Prior to the commencement of it internal operation, WIN0010 temporarily stores the control information to its Instruction Register (IR) and Data Register (DR) in order to easily facilitate interface with various types of MPU. The internal operations of the WIN0010 are determined by the signals (RS, R/WB, DB0 to DB7) that are sent from the MPU. These signals are categorized into 4 instructions types, namely:

- 1, Function Setting Instructions (i.e. Display, Format, Data Length etc.)

- 2. Internal RAM Address Setting Instructions

- 3. Data Transfer with Internal RAM Instructions

- 4. Miscellaneous Function Instructions

The generally used instructions are those that execute data transfers with the internal RAM. However, when the internal RAM addresses are auto incremented/decremented by 1 after each Data Write, the program load of the MPU is lightened. The Display Shift Instruction can be executed at the same time as the Display Data Write, thereby minimizing system development time with maximum programming efficiency.

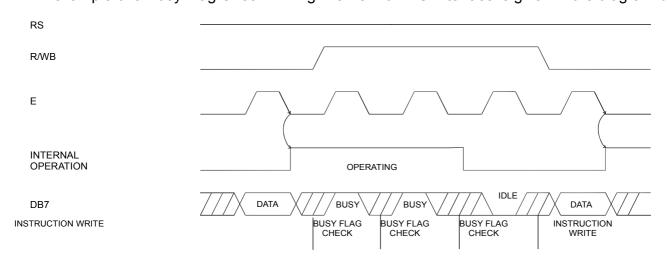

When an instruction is being executed for an internal operation, only the Busy Flag/Address Read Instruction can be performed. The other instructions are not valid. It should be noted that during the execution of an instruction, the Busy Flag is set to "1". The Busy Flag is set to "0" when the instructions are can be accepted and executed. Therefore, the Busy Flag should be checked to make certain that BF = "0" before sending another instruction from the MPU. If not, the time between the first instruction and the next instruction is longer than the time it takes to execute the instruction itself.

| Instruction                                 | Code |      |         |      |     |     | Max.<br>Execution<br>Time when |                                     |     |     |                                                                                                                                                                                     |                         |

|---------------------------------------------|------|------|---------|------|-----|-----|--------------------------------|-------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                             | RS   | R/WB | DB7     | DB6  | DB5 | DB4 | DB3                            | DB2                                 | DB1 | DB0 |                                                                                                                                                                                     | fsp or fosc =<br>250KHz |

| Clear Display                               | 0    | 0    | 0       | 0    | 0   | 0   | 0                              | 0                                   | 0   | 1   | Clears entire display.<br>Sets DDRAM Address 0 into the<br>Address Counter                                                                                                          | 6.2ms                   |

| Return Home                                 | 0    | o    | 0       | 0    | 0   | 0   | 0                              | 0                                   | 1   | 0   | Sets DDRAM Address 0 into the Address Counter. Returns shifted display to original position. DDRAM contents remain unchanged. (DB0 is test pin. User should set DB0=0 all the time) | 0                       |

| Entry Mode<br>Set                           | 0    | 0    | 0       | 0    | 0   | 0   | 0                              | 1                                   | I/D | s   | Sets cursor move direction and specifies display shift. (These operations are performed during data write and read.)                                                                | 0                       |

| Display<br>ON/OFF<br>Control                | 0    | 0    | 0       | 0    | 0   | 0   | 1                              | D                                   | С   | В   | Sets entire Display (D) ON/OFF.<br>Sets Cursor (C) ON/OFF.<br>Sets Blinking (B) of Cursor<br>Position Character.                                                                    | 0                       |

| Cursor/<br>Display Shift/<br>Mode/ Pwr      | 0    | 0    | 0       | 0    | 0   | 1   | S/C                            | R/L                                 | 0   | 0   | Moves cursor & shifts display without changing DDRAM contents.                                                                                                                      | 0                       |

|                                             |      |      |         |      |     |     | G/C                            | PWR                                 | 1   | 1   | Sets Graphic/Character Mode<br>Sets internal power on/off                                                                                                                           |                         |

| Function Set                                | 0    | 0    | 0       | 0    | 1   | DL  | N                              | F                                   | FT1 | FT0 | Sets interface data length (DL). Sets number of display lines (N). Sets Character Font (F). Sets Font Table (FT)                                                                    | 0                       |

| et CGRAM<br>Address                         | 0    | 0    | 0       | 1    | ACG | ACG | ACG                            | ACG                                 | ACG | ACG | Sets CGRAM Address. CGRAM data is sent and received after this setting.                                                                                                             |                         |

| et DDRAM<br>Address                         | 0    | 0    | 1       | ADD  | ADD | ADD | ADD                            | ADD                                 | ADD | ADD | Sets DDRAM Address. The DDRAM data Is sent and received after this setting.                                                                                                         | 0                       |

| lead Busy<br>Flag &<br>Address              | 0    | 1    | BF      | AC   | AC  | AC  | AC                             | AC                                  | AC  | AC  | Reads Busy Flag (BF) indicating that internal operation is being performed. Reads Address Counter contents.                                                                         | 0                       |

| Write data<br>into the<br>CGRAM or<br>DDRAM | 1    | 0    | Write D | ata  | •   | 1   | -                              | Writes data into the CGRAM or DDRAM | 0   |     |                                                                                                                                                                                     |                         |

| Read Data<br>from the<br>CGRAM or<br>DDRAM  | 1    | 1    | Read D  | )ata |     |     |                                |                                     |     |     | Read data from the CGRAM or DDRAM                                                                                                                                                   | 0                       |

#### Notes:

- 1. After the CGRAM/DDRAM Read or Write Instruction has been executed, the RAM Address Counter is incremented or decremented by 1. After the Busy Flag is turned OFF, the RAM Address is updated.

- 2. I/D=Increment/Decrement Bit

- I/D="1": Increment

- I/D="0": Decrement

- 3. S=Shift Entire Display Control Bit. When S="0", shift function disable.

- 4. BF=Busy Flag

- BF="1": Internal Operating in Progress

- BF="0": No Internal Operation is being executed, next instruction can be accepted.

- 5. R/L=Shift Right/Left

- R/L="1": Shift to the Right

- R/L="0": Shift to the Left

- 6. S/C=Display Shift/Cursor Move

- S/C="1": Display Shift

- S/C="0": Cursor Move

- 7. G/C=Graphic/Character mode selection. G/C="0", Character mode is selected. G/C="1", Graphic mode is selected.

- 8. PWR=Internal DCDC on/of control. PWR="1", DCDC on. PWR="0", DCDC off.

- 9. DDRAM=Display Data RAM

- 10. CGRAM=Character Generator RAM

- 11. ACG=CGRAM Address

- 12. ADD=Address Counter Address (corresponds to cursor address)

- 13. AC=Address Counter (used for DDRAM and CGRAM Addresses)

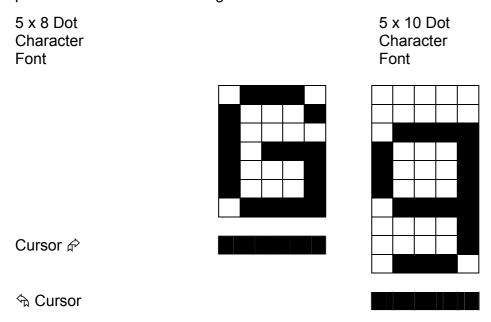

- 14. F=Character Pattern Mode

- F="1": 5 x 10 dots

- F="0": 5 x 8 dots

- 15. N=Number of Lines Displayed

- N="1": 2 -Line Display

- N="0": 1-Line Display

- 16. tADD is the time period starting when the Busy Flag is turned OFF up to the time the Address Counter is updated. Please refer to the diagram below.

# INSTRUCTION DESCRIPTION CLEAR DISPLAY INSTRUCTION

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

This instruction is used to clear the Display Write Space 20H in all DDRAM Addresses. That is, the character pattern for the Character Code 20H must be a BLANK pattern. It then sets the DDRAM Address 0 into the Address Counter and reverts the display to its original state (if the display has been shifted). The display will be cleared and the cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line 's left edge of the display.

Under the Entry Mode, this instruction also sets the I/D to 1 (Increment Mode). The S Bit of the Entry Mode does not change.

# **RETURN HOME INSTRUCTION**

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   |

Note: \* = Not Relevant

This instruction is used to set the DDRAM Address 0 into the Address Counter and revert the display to its original status (if the display has been shifted). The DDRAM contents do not change.

The cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line's left edge of the display.

# **ENTRY MODE SET INSTRUCTION**

The Entry Mode Set Instruction has two controlling bits: I/D and S. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

#### I/D IS THE INCREMENT/DECREMENT BIT.

When I/D is set to "1", the DDRAM Address is incremented by "1" when a character code is written into or read from the DDRAM. An increment of 1 will move the cursor or blinking one step to the right.

When I/D is set to "0", the DDRAM is decremented by 1 when a character code is written into or read from the DDRAM. A decrement of 1 will move the cursor or blinking one step to the left.

# S: SHIFT ENTIRE DISPLAY CONTROL BIT

This bit is used to shift the entire display. When S is set to "1", the entire display is shifted to the right (when I/D ="0") or left (when I/D ="1"). When S is set to "0", the display is not shifted.

Ex1: I/D=1, S=1

|   |   | 1 | 2 | 3 | 4 | _ | Initial display         |

|---|---|---|---|---|---|---|-------------------------|

|   | 1 | 2 | 3 | 4 | Α | _ | Input new character "A" |

| 1 | 2 | 3 | 4 | Α | В | _ | Input new character "B" |

| 2 | 3 | 4 | Α | В | С | _ | Input new character "C" |

| 3 | 4 | Α | В | С | D | _ | Input new character "D" |

Ex2: I/D=0, S=1

| Initial display         |   |   | _        | 4 | 3 | 2 | 1 |

|-------------------------|---|---|----------|---|---|---|---|

| Input new character "A" |   | Α | <u>4</u> | 3 | 2 | 1 |   |

| Input new character "B" | Α | В | <u>3</u> | 2 | 1 |   |   |

| Input new character "C" | В | С | 2        | 1 |   |   |   |

| Input new character "D" | С | D | 1        |   |   |   |   |

# DISPLAY ON/OFF CONTROL INSTRUCTION

The Display On / OFF Instruction is used to turn the display ON or OFF. The controlling bits are D, C and B.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

# D: DISPLAY ON/OFF BIT

When D is set to "1", the display is turned ON. When D is set to "0", the display is turned OFF and the display data is stored in the DDRAM. The display data can be instantly displayed by setting D to "1".

#### C: CURSOR DISPLAY CONTROL BIT

When C is set to "1", the cursor is displayed. In a  $5 \times 8$  dot character font, the cursor is displayed via the 5 dots in the 8th line. In a  $5 \times 10$  dot character font, it is displayed via 5 dots in the 11th line.

When C is set to "0", the cursor display is disabled.

During a Display Data Write, the function of the I/D and others will not be altered even if the cursor is not present. Please refer to the figure below.

# **B: BLINKING CONTROL BIT**

When B is set to '1", the character specified by the cursor blinks. The blinking feature is displayed by switching between the blank dots and the displayed character at a speed of 409.6ms intervals when the fcp or fosc is 250kHz. Please refer to the figure below.

Figure 1

Note: Figures 1 and 2 are alternately displayed

The cursor and the blinking can be set to display at the same time. The blinking frequency depends on the fosc or the reciprocal of fcp.

To illustrate, when fosc=TBD Hz, then, the blinking frequency=409.6 x 250/270=379.2ms

# CURSOR/DISPLAY SHIFT INSTRUCTION

This instruction is used to shift the cursor or display position to the left or right without writing or reading the Display Data. This function is used to correct or search the display. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 1   | S/C | R/L | 0   | 0   |